Product Summary

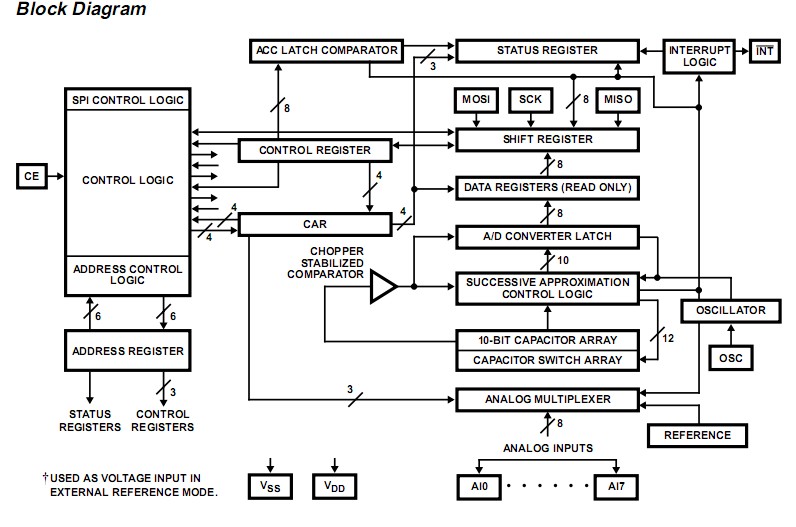

The CDP68HC68A2E is a CMOS 8-bit or 10-bit successive approximation analog to digital converter (A/D) with a standard Serial Peripheral Interface (SPI) bus and eight multiplexed analog inputs. Voltage referencing is user selectable to be relative to either VDD or analog channel 0 (AI0). The analog inputs of the CDP68HC68A2E can range between VSS and VDD. The CDP68HC68A2E employs a switched capacitor, successive approximation A/D conversion technique which provides an inherent sample-and-hold function. An onchip Schmitt oscillator provides the internal timing for the A/D converter. The Schmitt input can be externally clocked or connected to a single, external capacitor to form an RC oscillator with a period of approximately 10-30ns perpicofarad.

Parametrics

CDP68HC68A2E absolute maximum ratings: (1)DC Supply Voltage Range, (VDD): -0.5V to +7V (Voltage Referenced to VSS Terminal); (2)Input Voltage Range, All Inputs: -0.5V to VDD +0.5V; (3)DC Input Current, Any One Input: ±10mA; (4)Temperature Ambient, TA: -40 to 85℃; (5)DC Voltage Range: 3V Min, 6V Max.

Features

CDP68HC68A2E features: (1)10-Bit Resolution; (2)8-Bit Mode for Single Data Byte Transfers; (3)SPI (Serial Peripheral Interface) Compatible; (4)Operates Ratiometrically Referencing VDD or an External Source; (5)14μs 10-Bit Conversion Time; (6)8 Multiplexed Analog Input Channels; (7)Independent Channel Select; (8)Three Modes of Operation; (9)On Chip Oscillator; (10)Low Power CMOS Circuitry; (11)Intrinsic Sample and Hold; (12)16 Lead Dual-In-Line Plastic Package; (13)20 Lead Dual-In-Line Small Outline Plastic Package; (14)Evaluation Board available - CDP68HC05C16BEVAL.

Diagrams

|

CDP6402 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CDP6402C |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CDP6805E3E |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CDP6872 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CDP68HC68A2 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CDP68HC68P1 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))