Product Summary

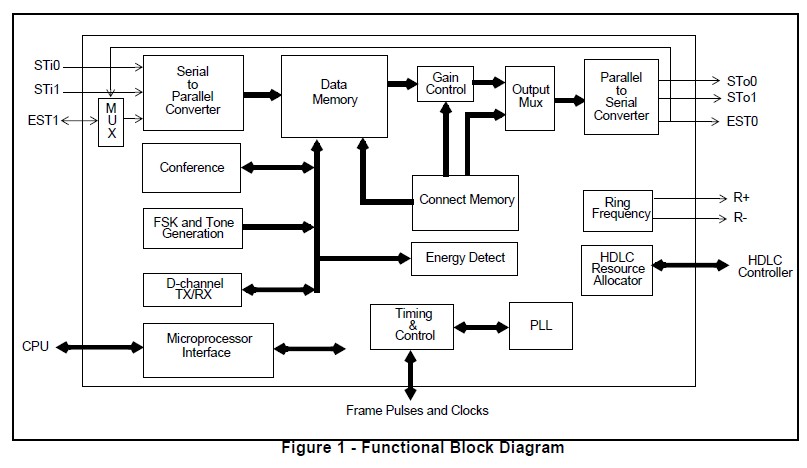

By integrating key functions needed in voice telecom application, the Integrated Digital Switch (IDX) MT90812ap provides a solution-on-a-chip for key telephone systems, PBX applications or CTI designs. The MT90812ap provides non-blocking timeslot interchange capability for B, C and D channels, up to a maximum of 192 channels. It offers conference call capability for 15 parties over a maximum of 5 conference bridges. With its integrated PLL, the MT90812ap provides the necessary clocks to support peripheral devices, such as codecs or interconnected IDX devices. Integrated into the IDX is the capability to detect supervisory signalling and to generate FSK 1200-baud signals. In addition, an integrated digital tone generator produces continuous dual tones, including standard DTMF. With its programmable gain control, the IDX MT90812ap allows users to use codecs without gain control and also centrally manage conference calls.

Parametrics

MT90812ap absolute maximum ratings: (1)VDD - VSS, VDD: - 0.3 to 7.0 V; (2)Voltage on any pin I/O (other than supply pins), VI/O: VSS - 0.3 to VDD + 0.3 V; (3)Current at any pin other than supply pins, IPIN: 40 mA max; (4)Package power dissipation, PD: 2 W; (5)Storage temperature, TS: - 65 to + 150 ℃.

Features

MT90812ap features: (1)192 channel x 192 channel non-blocking switching; (2)2 local bus streams @ 2Mb/s supports up to 64 channels; (3)In TDM mode, the expansion bus supports up to 128 channels at 8.192 Mb/s; (4)Rate conversion capability between local and expansion bus streams; (5)Integrated conference bridge, supporting 15 parties over 5 bridges; (6)Integrated PLL; (7)Frequency Shift Keying (FSK) 1200 baud transmitter, meeting Bell 202 or CCITT V.23; (8)standards; (9)32 channel dual tone generator, including 16 standard DTMF tones and tone ringer; (10)Expansion bus in IDX Link mode, allows the interconnection of up to 4 IDX devices; (11)Programmable per channel gain control from +3 to -27dB, increments of 1dB for output channels; (12)Supervisory signalling cadence detection capability; (13)HDLC resource allocator; (14)D-channel buffering of message information; (15)C-channel access for control and status registers; (16)Provides both variable and constant delay modes; (17)Parallel microprocessor port, compatible to Intel and Motorola and National CPU’s; (18)Supports both A-law or u-law operation; (19)Supports both ST-BUS, GCI and HMVIP framing formats.

Diagrams

|

MT900A-UR |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT90210 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT90210AL |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT90220 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT90220AL |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT90221 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))