Product Summary

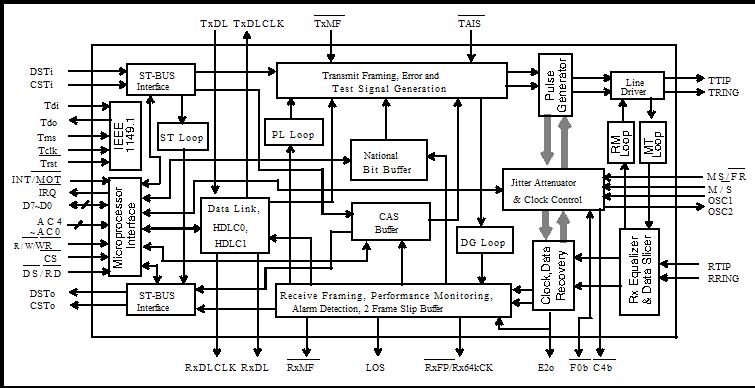

The MT9075BP is a single chip transceiver which integrates an advanced PCM 30 framer with a LineInterface Unit (LIU).The framer interfaces to a 2.048 Mbit/s backplane and provides selectable rate data link access with optional HDLC controllers for Sa bits and channel 16.The LIU interfaces the framer functions to the PCM30 transformer-isolated four wire line.The MT9075BP meets or supports the latest ITU-T Recommendations including G.703, G.704, G.706,G.732, G.775, G.796, G.823 for PCM 30, and I.431for ISDN primary rate. It also meets or supports ETSIETS 300 011, ETS 300 166 and ETS 300 233 as well as BS 6450. Applications include E1 add/drop multiplexers and channel banks, CO and PBX equipment interfaces, Primary Rate ISDN nodes and Digital Cross-connect Systems (DCS).

Parametrics

MT9075BP Absolute Maximum Ratings: (1)Supply Voltage: -0.3 to 7 V; (2)Voltage at Digital Inputs: -0.3 to VDD + 0.3 V; (3)Current at Digital Inputs: 30 mA; (4)Voltage at Digital Outputs: -0.3 to VDD + 0.3 V; (5)Current at Digital Outputs: 30 mA; (6)Storage Temperature: -55 to 125℃.

Features

MT9075BP features: (1)Combined PCM 30 framer, Line Interface Unit(LIU) and link controllers in a 68 pin PLCC or100 pin MQFP package; (2)Selectable bit rate data link access withoptional Sa bits HDLC controller (HDLC0) andchannel 16 HDLC controller (HDLC1); (3)LIU dynamic range of 20 dB; (4)Enhanced performance monitoring andprogrammable error insertion functions; (5)Low jitter DPLL for clock generation; (6)Operating under synchronized or free run mode; (7)Two-frame receive elastic buffer with controlledslip direction indication; (8)Selectable transmit or receive jitter attenuator; (9)Intel or Motorola non-multiplexed parallelmicroprocessor interface; (10)CRC-4 updating algorithm for intermediate pathpoints of a message-based data link application; (11)ST-BUS/GCI 2.048 Mbit/s backplane bus forboth data and signalling.

Diagrams

(China (Mainland))

(China (Mainland))